✨ Takeaways

- DDR4 SDRAM initialization involves a structured sequence of operations to prepare the memory for use.

- ZQ Calibration is crucial for ensuring data integrity and performance by tuning the resistance of DQ pins.

- Understanding these processes is essential for hardware engineers working with memory subsystems.

DDR4 SDRAM Initialization, Training, and Calibration: A Deep Dive

Understanding DDR4 Initialization

When powering up a device with a DDR4 SDRAM subsystem, a series of meticulously defined steps occur before the memory can be operational. According to the JEDEC specification, the initialization process comprises four distinct phases: Power-up and Initialization, ZQ Calibration, Vref DQ Calibration, and Read/Write Training. Each phase is critical in ensuring that the memory operates correctly and efficiently within the system.

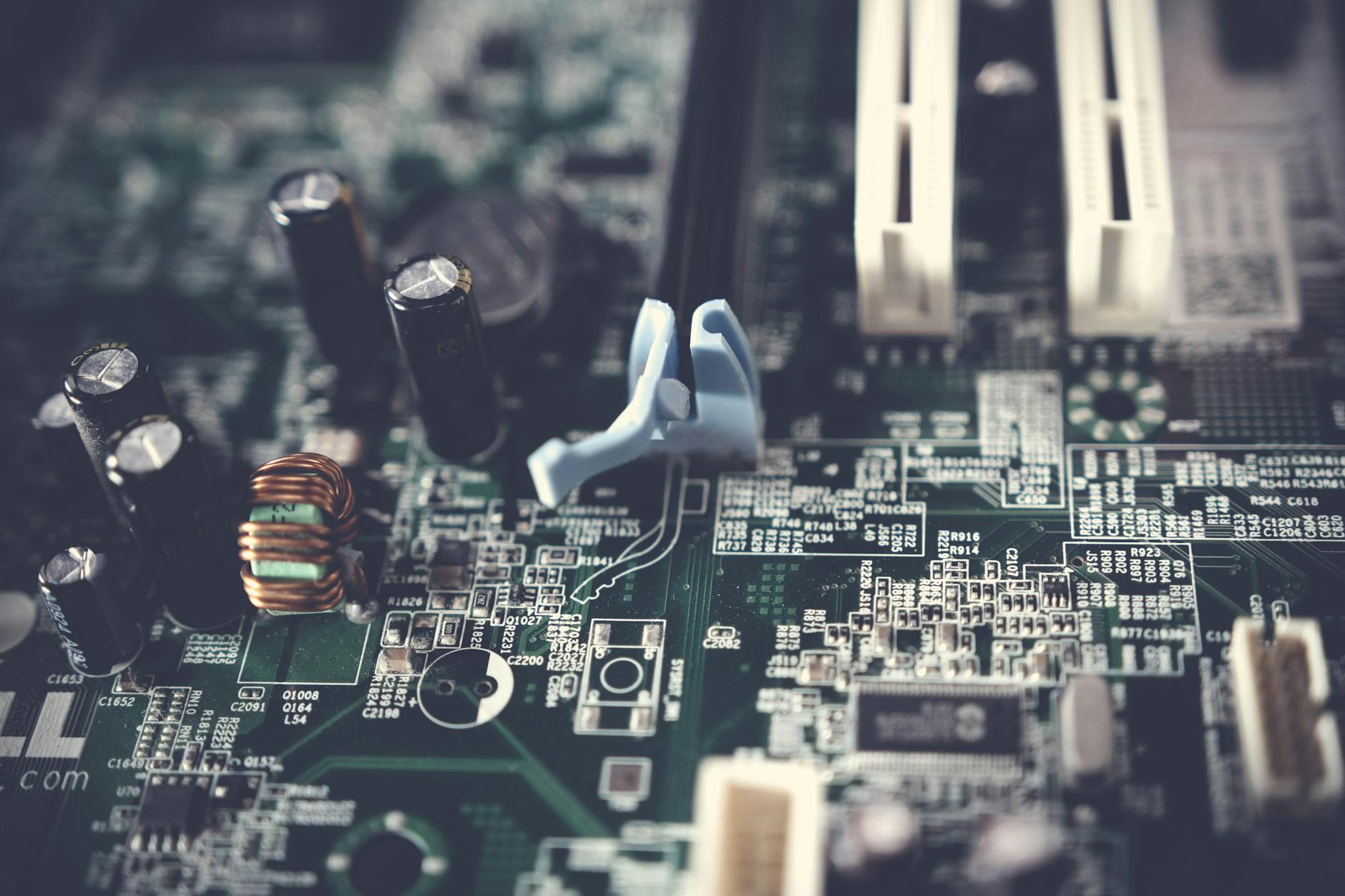

During the Power-up and Initialization phase, the controller in the ASIC, FPGA, or processor automatically executes a fixed sequence of commands. This includes applying power to the DRAM, de-asserting the reset signal, activating the clock, and issuing Mode Register Set (MRS) commands to configure the memory settings. By the end of this phase, the DDR4 memory understands its operational frequency and timing parameters, such as CAS Latency (CL) and CAS Write Latency (CWL). This foundational setup is crucial for the subsequent calibration and training phases.

The Importance of ZQ Calibration

One of the most critical steps in the DDR4 initialization process is ZQ Calibration, which ensures the accuracy of the data pins (DQ). Each DQ pin is bidirectional, responsible for both sending and receiving data. The inherent variability in the resistance of the DQ pin circuits—affected by temperature and voltage fluctuations—necessitates a calibration process to maintain data integrity.

To achieve this, each DRAM module includes a DQ calibration control block and a ZQ pin connected to an external precision resistor. This resistor, typically maintained at 240Ω, serves as a reference point during the calibration process. When a ZQ Calibration command (ZQCL) is issued, the control block produces a tuning value that is then applied to each DQ pin's internal circuitry. This ensures that all DQ pins operate at the desired resistance, thereby optimizing performance and reliability.

Implications for Hardware Engineers

For hardware engineers, understanding the intricacies of DDR4 initialization, training, and calibration is essential. These processes not only affect memory performance but also influence the overall system reliability. As memory speeds increase and applications demand more from hardware, the need for precise calibration becomes even more critical.

Moreover, the knowledge of how ZQ Calibration works can provide engineers with insights into troubleshooting memory-related issues. For instance, if a system experiences data corruption or performance degradation, it may be necessary to revisit the calibration settings or the integrity of the reference resistor. As the industry continues to evolve, mastering these foundational concepts will be key for engineers looking to push the boundaries of memory technology.